- 12. Repeat steps 1 through 11 for all other bits to be programmed in the PROM.

- Programming rejects returned to the factory must be accompanied by data giving address, desired data, and actual output data of the lo-

cation in which a programming failure has occured.

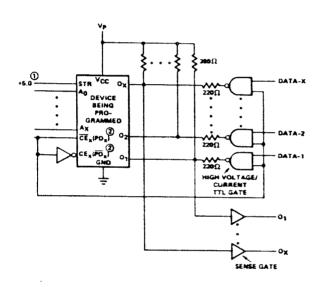

# **Typical Programming Circuit**

The circuit and timing diagrams shown in Figures 1 and 2 will establish the proper programming conditions for the output enable pulses. This allows the use of standard TTL parts for all logic inputs to the PROM. Note the gate which senses the output must withstand up to 11.0 volts during programming.

### FIGURE 1

- The strobe input must remain at VIH throughout the procedure. (for latched output devices only.)

- Disregard for devices with no enable inputs.

NOTE: For the 7629, pin 23 must remain at 5V during programming.

#

# FIGURE 2

Disregard for devices with no enable inputs.

The strobe input must remain at VIH throughout the procedure. (for latched output devices only.)

This timing diagram shows device terminal conditions. Each positive going data pulse at the terminal blows the corresponding bit, resulting in a low output for that bit. Therefore, a low input at the DATA-X points of the Figure 1 circuit results in a permanent low output of a bit.

GENEVE

. MÉTIERS .

DES ARTS

82S23-F,N • 82S123-F,N

### DESCRIPTION

The 82S23 and 82S123 are field programmable, which means that custom patterns are immediately available by following the fusing procedure given in this data sheet. The standard 82S23 and 82S123 devices are supplied with all outputs at logical low. Outputs are programmed to a logic high level at any specified address by fusing a Ni-Cr link matrix.

These devices include on-chip decoding and 1 chip enable input for ease of memory expansion. They feature either open collector or tri-state outputs for optimization of word expansion in bused organizations.

Both 82S23 and 82S123 devices are available in the commercial and military temperature ranges. For the commercial temperature range (0°C to +75°C) specify N82S23/123, N or F, and for the military temperature range (-55°C to +125°C) specify S82S23/123, F only.

### **FEATURES**

- Address access time: N82S23/123: 50ns max S82S23/123: 65ns max

- Power dissipation: 1.3mW/bit typ

- Input loading:

- N82S23/123: -100μA max S82S23/123: -150μA max

- On-chip address decoding

- Output options:

- 82S23: Open collector 82S123: Tri-state

- . No separate fusing pins

- Unprogrammed outputs are low level

- Fully TTL compatible

# **APPLICATIONS**

- Prototyping/volume production

- Sequential controllers

- Format conversion

- · Hardwired algorithms

- Random logic

- Code conversion

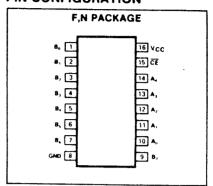

# PIN CONFIGURATION

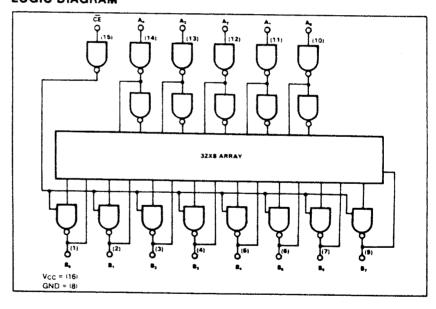

# LOGIC DIAGRAM

# **ABSOLUTE MAXIMUM RATINGS**

|      | PARAMETER          | RATING      | UNIT |  |

|------|--------------------|-------------|------|--|

| Vcc  | Supply voltage     | +7          | Vdc  |  |

| VIN  | Input voltage      | +5.5        | Vdc  |  |

|      | Output voltage     | l l         | Vdc  |  |

| Voh  | High (82S23)       | +5.5        |      |  |

| Vo   | Off-state (82S123) | +5.5        |      |  |

|      | Temperature range  |             | l ∘c |  |

| TA   | Operating          | 1           | •    |  |

|      | N82S23/123         | 0 to +75    |      |  |

|      | S82S23/123         | -55 to +125 |      |  |

| TSTG | Storage            | -65 to +150 | i    |  |

+ MATIERS - GRNBVE

DES ARTS

82S23-F,N • 82S123-F,N

DC ELECTRICAL CHARACTERISTICS N82S23/123:  $0^{\circ}$  C  $\leq$  T<sub>A</sub>  $\leq$  +75° C, 4.75V  $\leq$  V<sub>CC</sub>  $\leq$  5.25V \$82\$23/123: -55°C ≤ TA ≤ +125°C, 4.5V < VCC ≤ 5.5V

|                        | PARAMETER                                                                          | TEST CONDITIONS                                                                                                                         | N82S23/123 |        |                        | S82S23/123 |      |                         | T              |

|------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------------------------|------------|------|-------------------------|----------------|

|                        |                                                                                    |                                                                                                                                         | Min        | Typ2   | Max                    | Min        | Typ2 | Max                     | UNIT           |

| VIL<br>VIH<br>VIC      | Input voltage<br>Low<br>High<br>Clamp                                              | I <sub>IN</sub> = -18mA                                                                                                                 | 2.0        | -0.8   | 0.85<br>-1.2           | 2.0        | -0.8 | 0.8                     | V .            |

| Vor<br>Vor             | Output voltage<br>Low<br>High                                                      | lout = 16mA<br>CE = Low, lout = -2mA, High stored                                                                                       | 2.4        |        | 0.45                   | 2.4        | 0.0  | 0.5                     | V              |

| lic<br>lin             | Input current<br>Low<br>High                                                       | VIN = 0.45V<br>VIN = 5.5V                                                                                                               |            |        | -100<br>50             |            |      | -150<br>50              | μА             |

| lolk<br>lo(OFF)<br>los | Output current<br>Leakage (82S23)<br>Hi-Z state (82S123)<br>Short circuit (82S123) | CE = High, V <sub>CUT</sub> = 5.5V<br>CE = High, V <sub>OUT</sub> = 5.5V<br>CE = High, V <sub>OUT</sub> = 0.5V<br>V <sub>OUT</sub> = 0V | -20        |        | 40<br>40<br>-40<br>-90 | -20        |      | 50<br>50<br>-50<br>-100 | μΑ<br>μΑ<br>mA |

| lcc                    | Vcc supply current                                                                 |                                                                                                                                         | 1          | 65     | 77                     | 1          | 65   | 85                      | mA             |

| Cin<br>Cout            | Capacitance<br>Input<br>Output                                                     | $V_{CC} = 5.0V$ $V_{IN} = 2.0V$ $V_{OUT} = 2.0V$                                                                                        |            | 5<br>8 |                        |            | 5 8  | ,                       | ρF             |

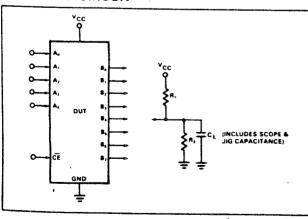

# AC ELECTRICAL CHARACTERISTICS $R_1$ = 270 $\Omega$ , $R_2$ = 600 $\Omega$ , $C_L$ = 30pF $^1$

N82S23/123:  $0^{\circ}$  C  $\leq$  T<sub>A</sub>  $\leq$  +75° C, 4.75V  $\leq$  V<sub>CC</sub>  $\leq$  5.25V

S82S23/123:  $-55^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  +125 $^{\circ}$ C, 4.5V  $\leq$  V<sub>CC</sub>  $\leq$  5.5V

| PARAMETER                        | то               | FROM                   | N82S23/123 |          |          | S82S23/123 |          |          | Ī    |

|----------------------------------|------------------|------------------------|------------|----------|----------|------------|----------|----------|------|

|                                  |                  |                        | Min        | Typ2     | Max      | Min        | Typ2     | Max      | UNIT |

| Access time TAA <sup>3</sup> TCE | Output<br>Output | Address<br>Chip enable |            | 35<br>25 | 50<br>35 |            | 35<br>25 | 65<br>40 | ns   |

| Disable time<br>T <sub>CD</sub>  | Output           | Chip disable           |            | 25       | 35       |            | 25       | 40       | ns   |

- 1. Positive current is defined as into the terminal referenced.

- Typical values are at V<sub>CC</sub> = 5.0V, T<sub>A</sub> = +25°C. 3 Tested at an address cycle time of 1µsec

# **TEST LOAD CIRCUIT**

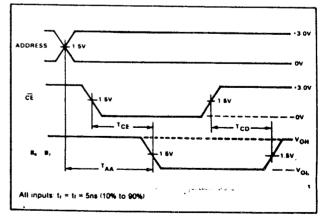

# **VOLTAGE WAVEFORM**

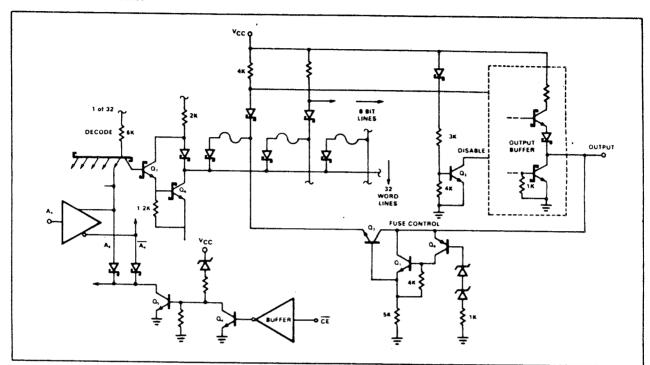

# 256 BIT BIPOLAR PROM (32X8)

#

82S23-F.N • 82S123-F.N

# PROGRAMMING SYSTEM SPECIFICATIONS<sup>4</sup> T<sub>A</sub> = 25°C. (Testing of these limits may cause programming of device.)

| PARAMETER        |                                                                   | TEST CONDITIONS                                              | LIMITS     |     |            |             |

|------------------|-------------------------------------------------------------------|--------------------------------------------------------------|------------|-----|------------|-------------|

|                  |                                                                   | 1231 CONDITIONS                                              | Min        | Тур | Max        | UNIT        |

| Vсср             | Power supply voltage<br>To program¹                               | I <sub>CCp</sub> = 425 ± 75mA,<br>Transient or steady state  | 8.5        |     | 9.0        | V           |

| Vccvh<br>Vccvl   | Verify limit Upper Lower                                          |                                                              | 5.3<br>4.3 |     | 5.7<br>4.7 | ٧           |

| Vs<br>ICCP       | Verify threshold <sup>2</sup> Programming supply current          | Vccp = +8 75 : 25V                                           | 1 4<br>350 |     | 1.6<br>500 | V<br>mA     |

| ViH<br>ViL       | Input voltage<br>High<br>Low                                      |                                                              | 2.4        |     | 5.5<br>0.8 | ٧           |

| lin<br>lit       | Input current<br>High<br>Low                                      | V <sub>1H</sub> = +5 5V<br>V <sub>1L</sub> = +0 4V           |            |     | 50<br>-500 | μА          |

| V <sub>OPF</sub> | Forced output voltage (program)3  Forced output current (program) | !OPF = 200 ± 20mA. Transient or steady state VOPF = +17 ± 1V | 16.0       |     | 18.0       | ٧           |

| TR               | Output pulse rise time                                            | AODE 11/ " 1A                                                | 10         |     | 220        | mΑ<br>μS    |

| tp               | CE programming pulse width                                        |                                                              | 100        |     | 125        | <b>μ</b> \$ |

| to               | Pulse sequence delay                                              |                                                              | 5          |     |            | μS          |

| tv               | CE verify pulse width                                             |                                                              | 1          |     |            | μS          |

| TPVA             | Address program-verify cycle                                      |                                                              |            |     | 1          | ms          |

| TPVM             | Memory program-verify time (continuous)                           |                                                              |            |     | 20         | sec         |

| FL               | Fusing attempts per link                                          | ,                                                            |            |     | 1          | cycle       |

### PROGRAMMING NOTES

- Bypass Vcc to GND with a 0.01 µF capacitor to reduce voltage spikes

- Vs is the sensing threshold of the PROM output voltage for a programmed bit. It normally constitutes

- the reference voltage applied to a comparator circuit to verify a successful fusing attempt. This voltage should be maintained within specified limits during the entire fusing cycle. For a transient current of 150mA, limit voltage spikes to a maximum slew rate of 2V/µs, and 10µs maximum

- These are specifications which a Programming System must satisfy in order to be qualified by Signetics. They contain new limits for minimizing total device programming time, which supersede but do not obsolete the performance requirements of previously manufactured programming equip-

# PROGRAMMING PROCEDURE

- 1. Terminate all device outputs with a 10kΩ resistor to  $V_{CC}$ . Apply  $\overline{CE}$  = High.

- 2. Select the Address to be programmed, and raise VCC to VCCP.

- 3. After to delay, apply VOPF to the output to be programmed. Program one output at the time.

- 4. After to delay, pulse the CE input to logic low for a time tp.

- After to delay, remove VOPF from the programmed output.

- Repeat steps 3 through 5 to program other bits at the same address.

- 7. To verify programming of all bits at the same address after to delay lower VCC to VCCVL and apply a logic low level to the

- CE input. All programmed outputs should remain in the logic high state.

- 8. After to delay, repeat steps 2 through 7 to program and verify all other address tocations.

- 9. After to delay raise VCC to VCCVH and verify all memory locations by applying a logic low level to  $\overline{CE}$ , and cycling through all device addresses.

86

# 256-BIT BIPOLAR PROM (32XE)

# 82872 (O.C.)/828123 (T.S.)

82S23-F,N • 82S123-F,N

# TYPICAL FUSING PATH

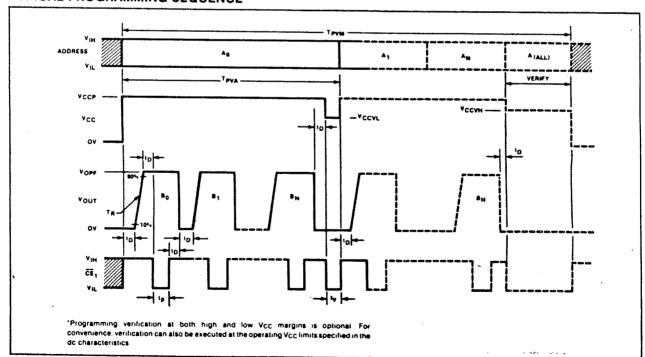

# TYPICAL PROGRAMMING SEQUENCE

# PROGRAMMABLE ARRAY LOGIC

Programming Features: PROMs (NiCr)

# **Programming Procedure**

- 1. Apply the desired address to the inputs.

- 2. Enable inputs may be left at any state.\*

- 3. Apply 5.5 V to V<sub>CC</sub>.

- 4. Apply  $V_{pp}$  to the program pin. (This step is not used on the 32 x 8 PROM).\*

- Apply VOUT to the output to be programmed (Program only one output at a time).

- 6. Remove VOUT.

- 7. Remove Vpp.

- Verification may be performed after each bit or word or after completing the programming of all memory locations.

- \*The 5330/1 and 6330/1 do not have a program pin. For these devices the output only is used in programming a particular selected bit and the device must be in the disabled state.

# **Optimized Programming Algorithm**

- 1. Pulse all fuses to be programmed with single, minimum voltage programming pulses (line 1 in the table).

- Verify all fuses at low VCC (4.2 V). During this step, unprogrammed fuses are pulsed up to eight more times (see table).

- 3. Re-verify at low  $V_{CC}$  (4.2 V) and high  $V_{CC}$  (6 V)

| Pulse<br>Number | Program Pin<br>Voltage | Output<br>Voltage |

|-----------------|------------------------|-------------------|

| 1 to 3          | 27 V                   | 20 V              |

| 4 to 6          | 30 V                   | 23 V              |

| 7 to 9          | 33 V                   | 26 V              |

### **Verification Procedure**

- 1. Enable the device.

- 2. To verify low-state:

- 2A. Apply an address where the output should be low.

- 2B. Apply 4.2 V to Vcc.

- 2C. Load the output with IQL = 12 mA.

- 2D. Check that the output is less than 0.8 V.

- 3. To verify High-state:

- 3A. Apply an address where the output should be high.

- 3B. Apply 6 V to VCC.

- 3C. Load the output with IOH = 0.3 mA.

- 3D. Check that the output is higher than 4.5 V.

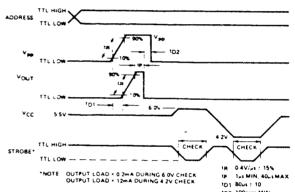

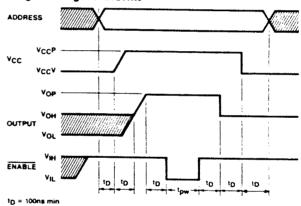

# **Programming Timing**

# Programming Parameters (Do not test these parameters or you will program the device)

| Symbol          | Parameter                           | Conditions<br>TA = +25 °C                  | Figure                                | Limits |     |     |      |

|-----------------|-------------------------------------|--------------------------------------------|---------------------------------------|--------|-----|-----|------|

|                 |                                     |                                            |                                       | Min    | Тур | Max | Unit |

| t <sub>R</sub>  | Slew rate of Programming Pulses +   |                                            |                                       | 0.3    |     | 0.5 | V/μs |

| VCCP            | VCC during Programming              |                                            |                                       | 5.4    | 5.5 | 5.6 | V    |

|                 | Maximum Duty Cycle                  |                                            | ··· · · · · · · · · · · · · · · · · · |        |     | 25  | %    |

| Vpp             | Programming Voltage on Program Pin* |                                            | 1                                     | 27     |     | 33  | V    |

| Vout            | Programming Voltage on Output Pin*  |                                            | 1                                     | 20     |     | 26  | V    |

| <sup>t</sup> D1 | Delay between V and V               |                                            |                                       | 0      | 10  | 20  | μs   |

| tD2             | peray permeen Abb and AOUT          | lay between Vpp and V <sub>OUT</sub> 1     |                                       | 0      | 0.5 | 1   |      |

| t <sub>p</sub>  | Pulse Width of VOUT                 |                                            | 1                                     | 10     |     | 25  | μs   |

| Volv            | VOL during verification             | Chip enabled<br>IOL = 12 mA<br>VCC = 4.2 V | 2                                     |        |     | 0.8 | V    |

| Vонv            | V <sub>OH</sub> during verification | Chip enabled<br>IOH = 0.3 mA<br>VCC = 6 V  | 2                                     | 4.5    |     |     | V    |

<sup>+</sup> Voltage supply must be capable of supplying at least 240 mA

<sup>\*</sup> Leading edge of Vpp and VOUT

# **PROGRAMMING**

Programming Features: PROMs (TiW)

# **Programming Description**

To program a particular bit normal TTL levels are applied to all inputs. Programming occurs when:

- 1. VCC is raised to an elevated level.

- The output to be programmed is raised to an elevated level.

- 3. The device is enabled.

In order to avoid misprogramming the PROM only one output at a time is to be programmed. Outputs not being programmed should be left open or connected to VCC (4.2 V to 6.2 V) via 5K  $\Omega$  resistors.

# **Programming Sequence**

The sequence of programming conditions is critical and must occur in the following order:

- 1. Select the appropriate address with chip disabled.

- 2. Increase V<sub>CC</sub> to programming voltage.

- Increase appropriate output voltage to programming voltage.

- 4. Enable chip for programming pulse width.

- 5. Decrease VOUT and VCC to normal levels.

# **Programming Timing**

In order to insure the proper sequence, a delay of 100 ns or greater must be allowed between steps. The enabling pulse must not occur less than 100 ns after the output voltage reaches programming level. The rise time of the voltage on VCC and the output must be between 1 and 10  $V/\mu s$ .

# Verification

After each programming pulse verification of the programmed bit should be made with both low and high VCC. The loading of the output is not critical and any loading within the DC specifications of the part is satisfactory.

### **Additional Pulses**

Up to 10 programming pulses should be applied until verification indicates that the bit has programmed. After verification an additional 5 programming pulses must be applied to insure the reliability of the programmed bit.

# **Programming Registered PROMs**

The asynchronous registered PROM is programmed in the same manner as standard PROMs.

The synchronous registered PROM is programmed in similar fashion with one exception: the program enable is registered and therefore must be blocked.

# **Programming Waveforms**

Figure 1

Note: Programming pulse t<sub>pw</sub> is applied for 5 additional pulses after verification indicates a bit is blown.

# Programming Parameters (Do not test these parameters or you may program the device)

| Symbol           | Parameter                               | R    | Recommended Value |                                                  |                       |  |  |

|------------------|-----------------------------------------|------|-------------------|--------------------------------------------------|-----------------------|--|--|

|                  |                                         | Min  | Тур               | Max                                              | Unit                  |  |  |

| V <sub>CCP</sub> | Required VCC for programming            | 10.5 | 11.0              | 11.5                                             | V                     |  |  |

| V <sub>OP</sub>  | Required output voltage for programming | 10.5 | 11.0              | 11.5                                             | $+\dot{v}$            |  |  |

| <sup>t</sup> R   | Rise time of VCC or VOUT                | 1.0  | 5.0               | 10.0                                             | V/µs                  |  |  |

| <sup>1</sup> CCP | Current limit of VCCP supply            | 800  | 1000              |                                                  | mA                    |  |  |

| IOP              | Current limit of VOP supply             | 15   | 20                | <del>                                     </del> | mA                    |  |  |

| tpw              | Programming pulse width (enabled)       | 9    | 10                | 11                                               | μs                    |  |  |

| Vcc              | Low VCC for verification                | 4.2  | 4,3               | 4.4                                              | V V                   |  |  |

| Vcc              | High VCC for verification               | 5.8  | 6.0               | 6.2                                              | T V                   |  |  |

| MDC              | Maximum duty cycle of VCCP              |      | 25                | 25                                               | <del>*</del>          |  |  |

| t <sub>D</sub>   | Delay time between programming steps    | 100  | 120               |                                                  | ns                    |  |  |

| VIL              | Input low level                         | 0    | 0                 | 0.5                                              | ''s                   |  |  |

| $v_{IH}$         | Input high level                        | 2.4  | 3.0               | 5.5                                              | $+\overset{v}{ec{v}}$ |  |  |